\*\*\*\*\*\*

## Boolean Algebra

There are some important rules must be considered to understand the Boolean algebra which are:

- **1-** A + 1 = 1, which does not mean addition operation, it means *OR* operation.

- 2 A + 0 = A

- **3-**  $\overline{A}$  means the inversion of *A*

- **4-**  $\overline{\overline{A}} = A$

- **5-** A + A = A

- **6-**  $A \cdot A = A$

- **7-**  $\bar{A} \cdot A = 0$

- **8-**  $\bar{A}$ + A =1

$9-A + \overline{A}B = A + B$

Ex3/ Prove that  $A + \overline{A}B = A + B$ .

Sol: take the right side

$A(1+B) + \overline{A}B = A + AB + \overline{A}B \{ \text{ since } (1+B) = 1 \}$

$$\rightarrow A + AB + \overline{AB} = A + B(A + \overline{A})$$

= A + B

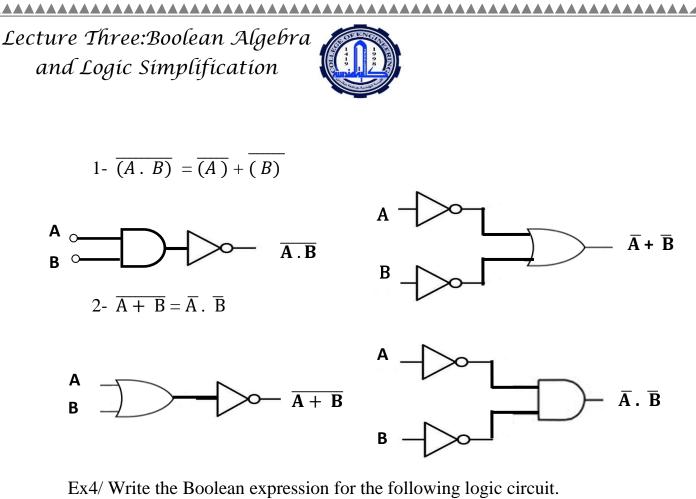

#### \* <u>De- Morgan's Theorem</u>

De-Morgan's Theorems are two additional simplification techniques, which used to simplify Boolean expressions. It is important to note that the more simple Boolean expression gives simple logic circuit.

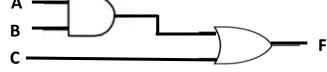

A -----

Sol:  $F = A \cdot B + C$

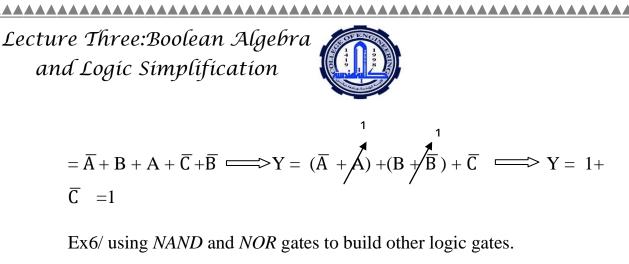

Ex 5/ Simplify the following Boolean algebra

$$\mathbf{Y} = \overline{\mathbf{A}} + \mathbf{A}\mathbf{B} + \mathbf{A}\mathbf{C}\mathbf{B} + \mathbf{C}\mathbf{A} + \overline{\mathbf{B}} + \overline{\mathbf{C}}$$

Sol:

Sol:

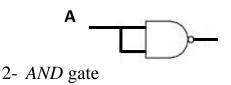

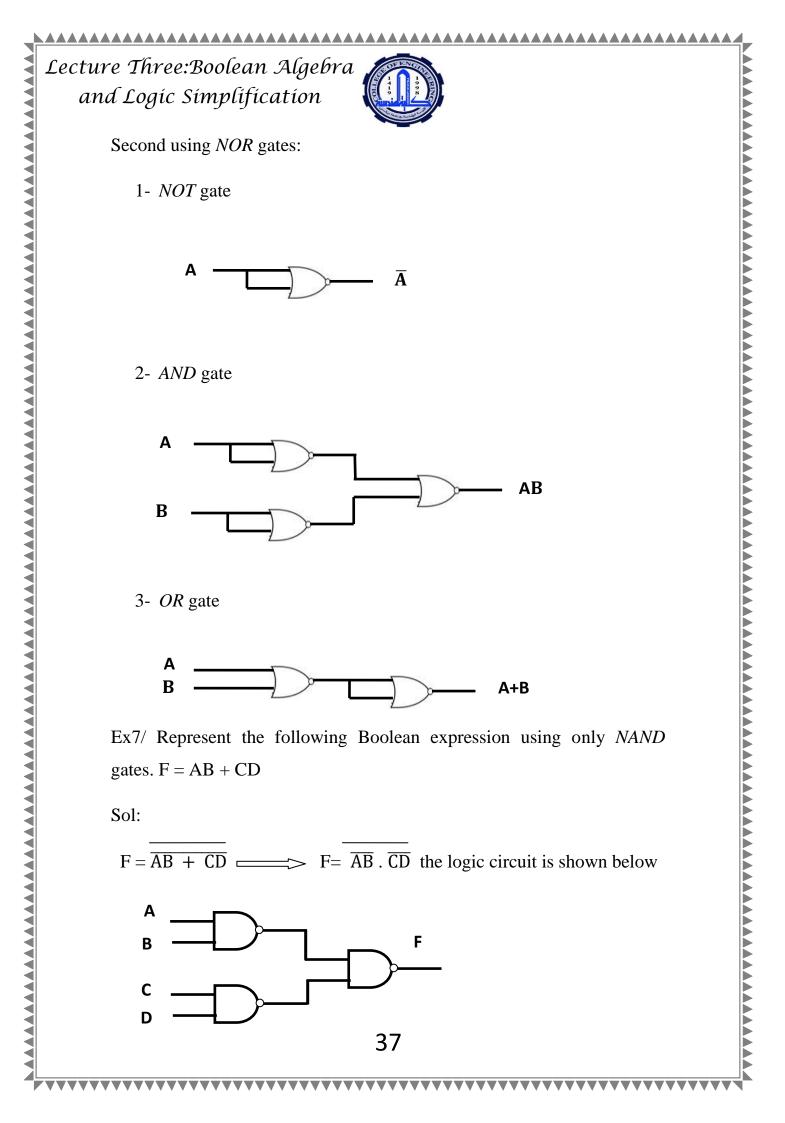

First using NAND gates:

1- NOT gate

*NOT* gate can be built easily by shorting the two terminal of the *NAND* gate.

AND gate can be obtained only by adding inverter NAND gate to the NAND gate as shown below.

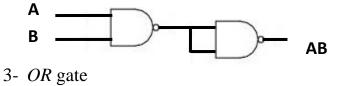

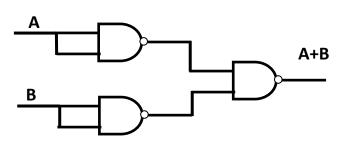

OR gate can be represented by three NAND gates.

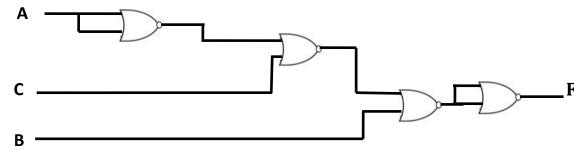

Ex8/draw the logic circuit to implement the following function {F = A  $\overline{C}$ +B} using *NOR* gates only.

\_\_\_\_\_

<u>HW1:</u> Build the following expression  $F = A \oplus B$ .

<u>HW2:</u> Implement F = ABC + AD using *NOR* gates only

HW3: Express [NOT, AND, and OR] gates using NOR gates only.

## \* <u>Primary Multiplication</u>

The primary multiplication is used to express the equivalent symbols of the truth table states, for example if there are four variables then the primary multiplication of { 000, 110, 111, and 001} is {  $\overline{ABC}$ ,  $AB\overline{C}$ ,  $AB\overline{C}$ ,  $AB\overline{C}$ ,  $ABC, \overline{ABC}$ }. This applied for two, four... etc.

## \* <u>Electronic logic circuits</u>

The logic circuits can be divided into two categories, combinational and sequential logic circuits. In the combinational logic circuit, the output depends on the inputs to the circuit while in the sequential logic circuit; the output depends on the inputs and the past value. To design the combinational logic circuits there are two methods, sum of product (*SoP*) and product of sum (*PoS*).

✤ <u>Sum of Product(SoP)</u>

To design any combinational logic circuit, the following steps must be applied.

- 1- Determine the numbers of inputs and outputs to the logic cct.

- 2- Draw the truth table of the logic cct.

- 3- Take the cases that gives ones logic (1) at the outputs.

\_\_\_\_\_

- 4- Write the primary multiplication of the inputs that give logic (1) outputs, each logic (1) inputs represent without dash(-) while each (0) represent with dash.

- 5- Add primary multiplication to each other to obtain the canonical form (*SoP*), and then simplify the final expression.

Ex 9/ Draw the logic circuit which has the following truth table.

|          | I/P      |          |          |

|----------|----------|----------|----------|

|          |          |          | O/P      |

| <u>A</u> | <u>B</u> | <u>C</u> | <u>Y</u> |

| 0        | 0        | 0        | 0        |

| 0        | 0        | 1        | 1        |

| 0        | 1        | 0        | 0        |

| 0        | 1        | 1        | 0        |

| 1        | 0        | 0        | 0        |

| 1        | 0        | 1        | 0        |

| 1        | 1        | 0        | 0        |

| 1        | 1        | 1        | 1        |

|          |          |          |          |

|          |          |          |          |

Sol: To design the logic circuit, the simplified Boolean expression must be found.

\*\*\*\*\*

$Y = \overline{A}\overline{B}C + ABC \implies Y = C (\overline{A}\overline{B} + AB)$

\_ C (A ● B )

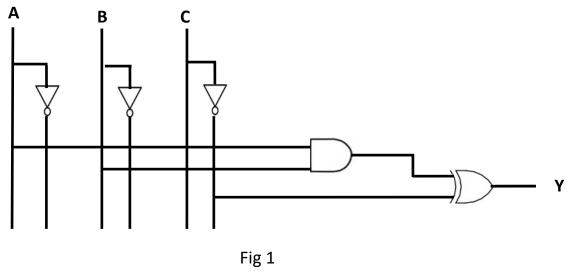

The logic circuit is shown in figure (1):

✤ <u>Product of Sum (PoS)</u>

The product of sum is another way to simplify the Boolean expression of any function. In this method zeros is taken instead of ones. It must be noted that the final expressions of the outputs for (*SoP*) and (*PoS*) are the same as will be illustrated in example (9).

Ex10/ Find the outputs of the following truth table by using (SoP) and (PoS).

| <u>A</u> | <u>B</u> | <u>Y</u> |

|----------|----------|----------|

| 0        | 0        | 1        |

| 0        | 1        | 0        |

| 1        | 0        | 1        |

| 1        | 1        | 1        |

|          |          |          |

Sol:

For (SoP)

$$Y = \Sigma (0, 2, 3) = \overline{A} \overline{B} + A\overline{B} + AB$$

$$= A (\overline{B} + B)^{1} + \overline{A} \overline{B}$$

$= A + \overline{A} \overline{B}$

$=(\overline{A}+B)$  { See Boolean Algebra point 9}

For (PoS)

$Y = \pi(0)$

$$= (\overline{A} + B)$$

Ex11/ Convert then simplify the following Boolean expression from (PoS) to (SoP).

$$\mathbf{Y} = (\mathbf{A} + \mathbf{B} + \overline{\mathbf{C}})(\overline{\mathbf{A}} + \mathbf{B} + \overline{\mathbf{C}})$$

Sol: easily by multiplying the two brackets by each other then

$$Y = [A\overline{A} + AB + A\overline{C} + B\overline{A} + BB + B\overline{C} + \overline{C}\overline{A} + \overline{C}B + \overline{C}\overline{C}]$$

$$= B(A+\overline{A}) + \overline{C} (A+\overline{A}) + B(1+\overline{C}) + \overline{C}(1+B)$$

$= B + \overline{C} + B + \overline{C}$   $\longrightarrow$   $Y = B + \overline{C}$

Ex11/ design a logic circuit that multiply two words with (2bits)

Sol:

Let first word (A) and the second words (B) then the truth table will be

.....

| $\underline{A_1}\underline{A_2}$ | $\underline{B_1}\underline{B_2}$ | $\underline{W} \underline{X} \underline{Y} \underline{Z}$ |

|----------------------------------|----------------------------------|-----------------------------------------------------------|

| 0 0                              | 0 0                              | 0 0 0 0                                                   |

| 0 0                              | 01                               | 0 0 0 0                                                   |

| 0 0                              | 10                               | 0 0 0 0                                                   |

| 0 0                              | 11                               | 0 0 0 0                                                   |

| 0 1                              | 0 0                              | 0 0 0 0                                                   |

| 0 1                              | 01                               | 0 001                                                     |

| 0 1                              | 10                               | 0 010                                                     |

| 0 1                              | 11                               | 0 011                                                     |

| 1 0                              | 0 0                              | 0 0 0 0                                                   |

| 1 0                              | 01                               | 0 010                                                     |

| 1 0                              | 10                               | 0 100                                                     |

| 1 0                              | 11                               | 0 110                                                     |

| 1 1                              | 0 0                              | 0 0 0 0                                                   |

| 1 1                              | 01                               | 0 0 1 1                                                   |

| 1 1                              | 10                               | 0 1 1 0                                                   |

| 1 1                              | 11                               | 1 0 0 1                                                   |

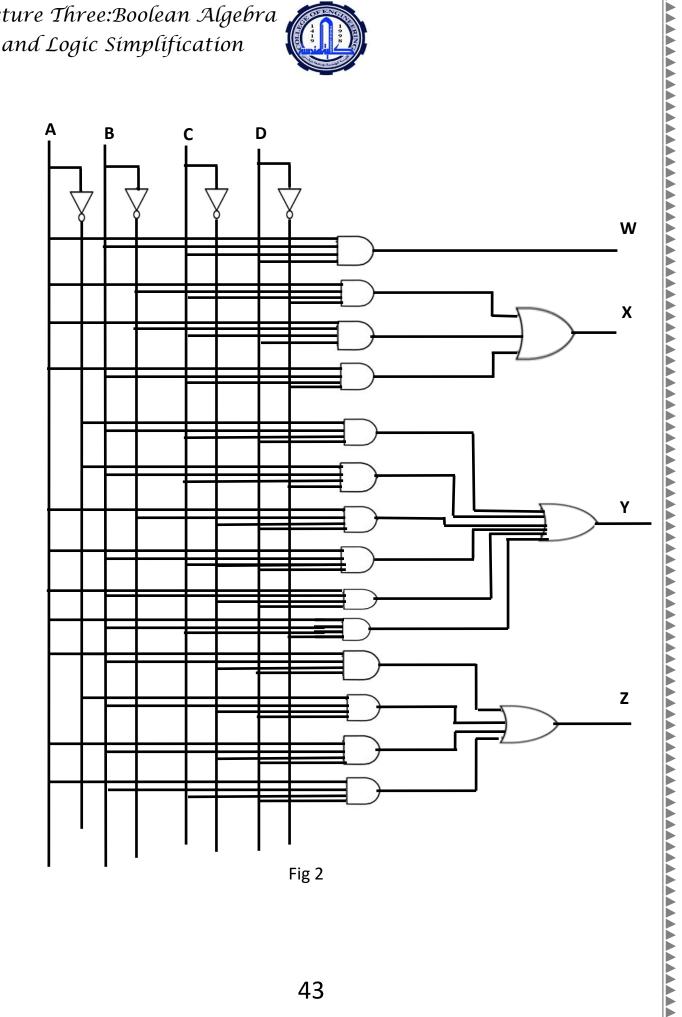

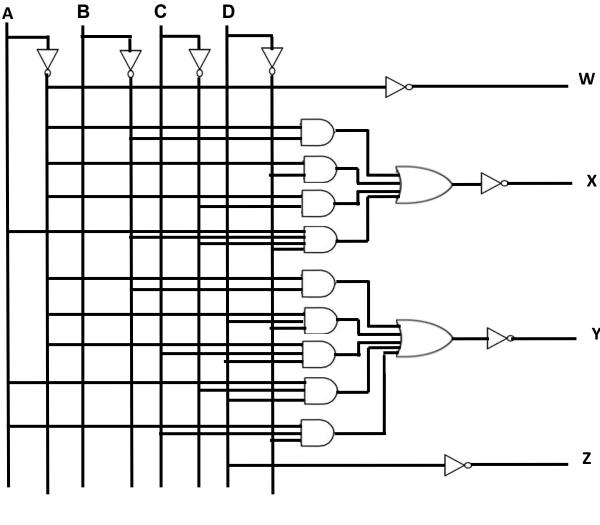

The equations of the output are given below:

$W = ABCD, \qquad X = A\overline{B}C\overline{D} + A\overline{B}CD + ABC\overline{D}$

$Y = \overline{A}BCD + \overline{A}BC\overline{D} + A\overline{B}\overline{C}D + A\overline{B}CD + AB\overline{C}D + ABC\overline{D}$

$Z = A\overline{B}\overline{C}D + \overline{A}BCD + AB\overline{C}D + ABCD$

The final step of the design is the drawing of the logic gate circuit as shown in figure (2)

43

V V V

\_\_\_\_\_

# \* Karnaugh Maps (K- Maps)

This is a graphical approach to finding suitable product terms for using sum of product expressions. The map is useful for problems of up to six variables and is particularly straightforward for most problems of three or four variables. Although there is no guarantee of finding a minimum solution, the methods we will develop nearly always produce a minimum. The main difference between Boolean simplification and (*K*-*Map*) is that (*K*-*Map*) gives the most simplified expression for the output of the truth table. There are many types of (*K*-*Maps*) depending on the numbers of inputs.

1- Two inputs

2- Three input

For two variables *A* and *B* the (*K*- *Map*) is given below for the following truth table

| NOS. | А              | В             | ВА | Ā | Α |   |

|------|----------------|---------------|----|---|---|---|

| 0    | <u>11</u><br>0 | <u>D</u><br>0 | В  | 0 | 2 |   |

| 1    | 0              | 1             | B  | 1 | 3 |   |

| 2    | 1              | 0             |    |   |   | _ |

| 3    | 1              | 1             |    |   |   |   |

The truth table and (K- Map) for three inputs is given below

| AB     | $\overline{A}\overline{B}$ | $\overline{A}$ B | AB | $A\overline{B}$ |

|--------|----------------------------|------------------|----|-----------------|

| с<br>7 | 0                          | 2                | 6  | 4               |

| С      | 1                          | 3                | 7  | 5               |

| NOS. | <u>A</u>       | <u>B</u> | <u>C</u> |  |  |  |  |

|------|----------------|----------|----------|--|--|--|--|

| 0    | 0              | 0        | 0        |  |  |  |  |

| 1    | 0              | 0        | 1        |  |  |  |  |

| 2    | 0              | 1        | 0        |  |  |  |  |

| 3    | 0              | 1        | 1        |  |  |  |  |

| 4    | 1              | 0        | 0        |  |  |  |  |

| 5    | 1              | 0        | 1        |  |  |  |  |

| 6    | 1              | 1        | 0        |  |  |  |  |

| 7    | 1              | 1        | 1        |  |  |  |  |

| 3-   | 3- Four inputs |          |          |  |  |  |  |

The truth table and (K- Map) for four inputs is given below

| NOS. | <u>A</u> | <u>B</u> | <u>C</u> | <u>D</u> |                            |                            |   |

|------|----------|----------|----------|----------|----------------------------|----------------------------|---|

| 0    | 0        | 0        | 0        | 0        |                            |                            |   |

| 1    | 0        | 0        | 0        | 1        | AB                         | $\overline{A}\overline{B}$ |   |

| 2    | 0        | 0        | 1        | 0        | $\overline{C}\overline{D}$ | 0                          |   |

| 3    | 0        | 0        | 1        | 1        | <b>¯</b> CD                |                            | ┢ |

| 4    | 0        | 1        | 0        | 0        | ĊĎ                         | 1                          |   |

| 5    | 0        | 1        | 0        | 1        | CD                         | 2                          |   |

| 6    | 0        | 1        | 1        | 0        | C₽                         |                            |   |

| 7    | 0        | 1        | 1        | 1        | CD                         | 3                          |   |

| 8    | 1        | 0        | 0        | 0        |                            |                            |   |

| 9    | 1        | 0        | 0        | 1        |                            |                            |   |

| 10   | 1        | 0        | 1        | 0        |                            |                            |   |

| 11   | 1        | 0        | 1        | 1        |                            |                            |   |

| 12   | 1        | 1        | 0        | 0        |                            |                            |   |

| 13   | 1        | 1        | 0        | 1        |                            |                            |   |

|      |          |          |          |          |                            |                            |   |

|                                                                                                                                                                     | $\overline{A}\overline{B}$ | $\overline{A}$ B | AB | $A\overline{B}$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|----|-----------------|

| <u><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/><u></u><br/></u> | 0                          | 4                | 12 | 8               |

| <b>C</b> D                                                                                                                                                          | 1                          | 5                | 13 | 9               |

| CD                                                                                                                                                                  | 2                          | 6                | 15 | 11              |

| C₽                                                                                                                                                                  | 3                          | 7                | 14 | 10              |

45

\_\_\_\_\_

- 14 1 1 1 0

- 15 1 1 1

- ✤ Important Notes:

1

- 1- To find the Boolean, the neighboring ones are taken with each other's.

- 2- Using (*K Map*) to find the outputs gives the most simplified expression.

- 3- There are some cases cannot be obtained in real case such as the presence of (1101) in (BCD) or (<) and (>) at the same time. These cases are called don't care cases which is denoted by (x).

- 4- The value of (*x*) can be one or zero depend on the neighboring cells in the (*K Map*).

- 5- *K Map* can be used with (*PoS*) by taking the neighboring zeros instead of ones to obtain inverting of output function, then taking the compliment of result to find the final outputs.

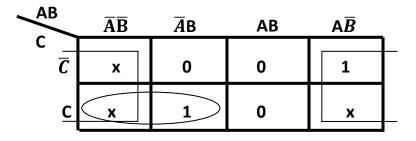

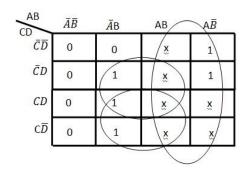

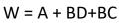

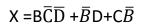

Ex12/ for the following (K- Maps) find the outputs expressions.

1- Three inputs

The output equation is

$\mathbf{Y} = \overline{\mathbf{B}} + \overline{\mathbf{A}}\mathbf{C}$

\_\_\_\_\_

|                                                                                                                                     | $\overline{A}\overline{B}$ | ĀB | AB | AB |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----|----|----|

| <del></del><br><del> </del> <del> </del> | ×                          | x  | 1  | 1  |

| <b>C</b> D                                                                                                                          | х                          | 0  | 0  | 0  |

| CD                                                                                                                                  | x                          | х  | 1  | x  |

| C⊅                                                                                                                                  | ×                          | x  | 1  | x  |

|                                                                                                                                     |                            |    |    |    |

From K- Map it can be obtained that

$\mathbf{Y} = \mathbf{C} + \overline{\mathbf{D}}$

Ex13/ design a logic circuit for the following

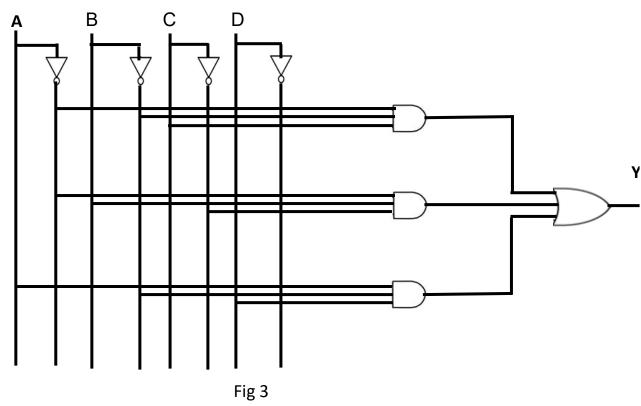

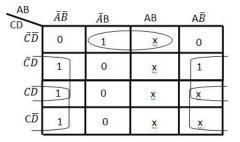

$Y = \Sigma(2, 3, 5, 9)$

Don't care =  $\Sigma$  (4, 12, 14, 15, 11)

Sol:

SoP is used in this equation, then the truth table and K- Map is given as

| <u>A</u> | <u>B</u> | <u>C</u> | <u>D</u> | <u>Y</u> |            | $\overline{A}\overline{B}$ | $\overline{A}$ B | AB | $A\overline{B}$ |

|----------|----------|----------|----------|----------|------------|----------------------------|------------------|----|-----------------|

| 0        | 0        | 0        | 0        | 0        | Ē          | 0                          | x                | x  | 0               |

| 0        | 0        | 0        | 1        | 0        | <b>C</b> D |                            |                  |    | $\land$         |

| 0        | 0        | 1        | 0        | 1        | υD         | 0                          |                  | 0  |                 |

| 0        | 0        | 1        | 1        | 1        | CD         |                            | 0                | x  | <b>x</b> /      |

| 0        | 1        | 0        | 0        | Х        | _          |                            |                  |    |                 |

| 0        | 1        | 0        | 1        | 1        | CD         |                            | 0                | X  | 0               |

\*\*\*\*\*\*\*\*\*

| 0 | 1 | 1 | 0 | 0 |

|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | Х |

| 1 | 1 | 0 | 0 | Х |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | Х |

| 1 | 1 | 1 | 1 | Х |

|   |   |   |   |   |

The equation of the logic circuit is  $[Y = \overline{ABC} + \overline{ABC} + \overline{ABD}]$  and the logic circuit is given in figure (3)

$Ex_{14}$ / design a logic circuit that has the following equations

$F_1 = \pi (2,3), F_2 = \Sigma (2,3).$

\*\*\*\*\*\*\*

Sol:

By assuming that the inputs are (A and B) the equations  $(F_1, F_2)$  can be written as:

$F_1 = (A + \overline{B})(A+B)$

$= A + A\overline{B}$

= A

$F_2 = A\overline{B} + AB$

= A

This means that  $F_1 = F_2$ , the logic circuits that gives  $F_1$  and  $F_2$  are given below

$\begin{array}{c} \mathbf{A} \\ \mathbf{F} \\ \mathbf{$

\*\*\*\*\*\*\*\*\*\*

<u>HW4:</u> using *K*- *Map* to find the simplified expression for the following function, and then draw the logic circuit that implements it in both methods using PoS with Boolean algebra and *SoP* with *K*- *Map*

F =  $\pi$  [1, 2, 4] & don't care is [5,7]

\*\*\*\*\*

Ex 15/ design a logic circuit that converts from (*BCD*) code to (*Excess – three*) code.

Sol: The truth table has four inputs and four outputs

|          | inj      | puts     |   |   | out      | puts     |          |

|----------|----------|----------|---|---|----------|----------|----------|

| <u>A</u> | <u>B</u> | <u>C</u> | D | W | <u>X</u> | <u>Y</u> | <u>Z</u> |

| 0        | 0        | 0        | 0 | 0 | 0        | 1        | 1        |

| 0        | 0        | 0        | 1 | 0 | 1        | 0        | 0        |

| 0        | 0        | 1        | 0 | 0 | 1        | 0        | 1        |

| 0        | 0        | 1        | 1 | 0 | 1        | 1        | 0        |

| 0        | 1        | 0        | 0 | 0 | 1        | 1        | 1        |

| 0        | 1        | 0        | 1 | 1 | 0        | 0        | 0        |

| 0        | 1        | 1        | 0 | 1 | 0        | 0        | 1        |

| 0        | 1        | 1        | 1 | 1 | 0        | 1        | 0        |

| 1        | 0        | 0        | 0 | 1 | 0        | 1        | 1        |

| 1        | 0        | 0        | 1 | 1 | 1        | 0        | 0        |

| 1        | 0        | 1        | 0 | Х | Х        | Х        | Х        |

| 1        | 0        | 1        | 1 | Х | Х        | Х        | Х        |

| 1        | 1        | 0        | 0 | Х | Х        | Х        | Х        |

| 1        | 1        | 0        | 1 | Х | Х        | Х        | Х        |

| 1        | 1        | 1        | 0 | Х | Х        | Х        | Х        |

| 1        | 1        | 1        | 1 | Х | Х        | Х        | Х        |

|          |          |          |   |   |          |          |          |

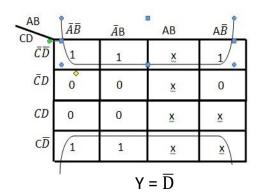

| CD | ĀĒ | Āв | AB | AĒ |  |  |

|----|----|----|----|----|--|--|

| Ē  |    | 1  | x  | P  |  |  |

| ĒD | 0  | 0  | ×  | 0  |  |  |

| CD | 1  | 1  | ×  | X  |  |  |

| C₽ | 0  | 0  | ×  | ×  |  |  |

$x = \overline{CD} + CD$

HW5: design a logic circuit that converts (BCD) to (7 - segment)

\_\_\_\_\_

<u>HW6:</u> design a logic circuit that compares between two words each one of them consists two bits in *Excess* – *three* codes.

<u>HW7</u>: design a logic circuit that gives an even and odd parity for *Excess* – *three* codes inputs.

Ex16/ find the logic circuit of the following {  $F=\Sigma(2,4,5,6)$ }, and {don't care =  $\prod (0,7)$  } using *K*- *Map PoS* minimization.

Sol: the truth table is and K - Map are shown below

The logic circuit is that implement function (F) can be drawn as figure

.........

Ex17/ design a logic circuit that converts (*Excess – three*) code to (2421) code, using K - Map with *PoS* minimization.

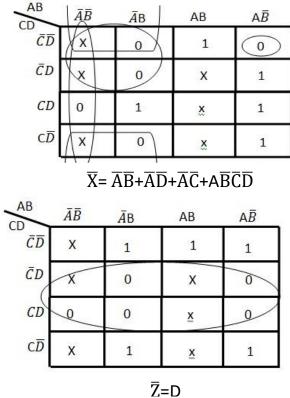

Sol: the truth table and K - Map are shown below

.....

| <u>A</u> | <u>B</u>   | <u>C</u>         | <u>D</u>     |    | W | <u>X</u> | <u>Y</u> | <u>Z</u> |  |

|----------|------------|------------------|--------------|----|---|----------|----------|----------|--|

| 0        | 0          | 1                | 1            |    | 0 | 0        | 0        | 0        |  |

| 0        | 1          | 0                | 0            |    | 0 | 0        | 0        | 1        |  |

| 0        | 1          | 0                | 1            |    | 0 | 0        | 1        | 0        |  |

| 0        | 1          | 1                | 0            |    | 0 | 0        | 1        | 1        |  |

| 0        | 1          | 1                | 1            |    | 0 | 1        | 0        | 0        |  |

| 1        | 0          | 0                | 0            |    | 1 | 0        | 1        | 1        |  |

| 1        | 0          | 0                | 1            |    | 1 | 1        | 0        | 0        |  |

| 1        | 0          | 1                | 0            |    | 1 | 1        | 0        | 1        |  |

| 1        | 0          | 1                | 1            |    | 1 | 1        | 1        | 0        |  |

| 1        | 1          | 0                | 0            |    | 1 | 1        | 1        | 1        |  |

| AB       |            | $\bar{4}\bar{B}$ | 721          |    |   |          | 5        |          |  |

| CD       |            | 48               | ĀB           | AB | 5 | AĒ       | ,<br>    |          |  |

| ĒĪ       | 2/         | X                | 0            | 8  | 1 | 1        |          |          |  |

| ĒĿ       | $^{\circ}$ | х                | 0            | )  | ( | 1        | 9        |          |  |

| CL       |            | 0                | 0            | X  |   | 1        |          |          |  |

| CĪ       | 5 \        | x                | 9            | ŷ  | ç | 1        |          |          |  |

| AD       |            | /                | <b>W</b> = 2 | Ā  |   | 0        |          |          |  |

| 4.0                                                                                                                                           |    | $\overline{W} = \overline{A}$ | Ā  |    |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------|----|----|--|

| CD                                                                                                                                            | AB | ĀВ                            | AB | AB |  |

| ĒD                                                                                                                                            | X  | 0                             | 1  | 1  |  |

| ĒD                                                                                                                                            | x  | 1                             | X  | 0  |  |

| CD                                                                                                                                            | 0  | 0                             | x  | 1  |  |

| CD                                                                                                                                            | x/ | 1                             | x  | 0  |  |

| 2                                                                                                                                             |    |                               |    |    |  |

| $\overline{Y}$ = $\overline{A}\overline{B}$ + $\overline{A}\overline{C}\overline{D}$ + $\overline{A}CD$ + $A\overline{C}D$ + $AC\overline{D}$ |    |                               |    |    |  |

\_\_\_\_\_

The logic circuit can be drawn as in the (*SoP*) case except that not gate is putting on the final logic gate to obtain the inverting of  $(\overline{A} \ \overline{B} \ \overline{C} \ \overline{D})$ .

<u>HW6:</u> design a logic circuit that finds the primary numbers from the following {0  $\longrightarrow$  15} using (*K*- *Map*) with *PoS* minimization.

<u>HW7:</u> design a logic circuit that divides numbers from (0) to (15) by two (2), gives (*ones*) outputs when the division operation has no carry and

\*\*\*\*\*

\*\*\*\*\*\*\*\*

(zeros) outputs when the division operation has carry using (K- Map) with PoS minimization.

<u>HW8:</u> design a logic circuit that compares two words each one of them has two bits using (K- Map) with PoS minimization.